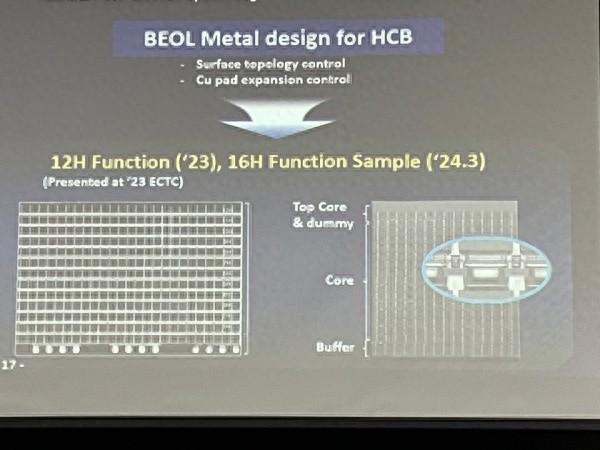

4 月 7 日消息,綜合韓媒 The Elec 和 ETNews 報道,三星電子先進封裝團隊高管 Dae Woo Kim 在 2024 年度韓國微電子與封裝學會年會上表示近日完成了采用 16 層混合鍵合 HBM 內存技術驗證。

Dae Woo Kim 表示,三星電子成功制造了基于混合鍵合技術的 16 層堆疊 HBM3 內存,該內存樣品工作正常,未來 16 層堆疊混合鍵合技術將用于 HBM4 內存量產。

▲ 圖源 The Elec,下同

相較現有鍵合工藝,混合鍵合無需在 DRAM 內存層間添加凸塊,而是將上下兩層直接銅對銅連接,可顯著提高信號傳輸速率,更適應 AI 計算對高帶寬的需求。

混合鍵合還可降低 DRAM 層間距,進而減少 HMB 模塊整體高度,但也面臨成熟度不足,應用成本昂貴的問題。

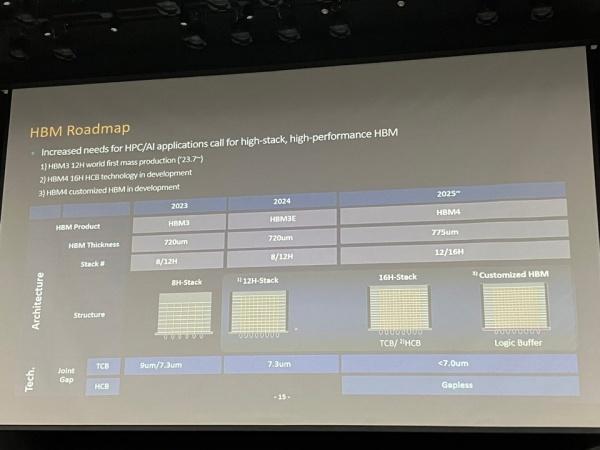

三星電子在 HBM4 內存鍵合技術方面采用兩條腿走路的策略,同步開發混合鍵合和傳統的 TC-NCF 工藝。

結合下方圖片和IT之家以往報道,HBM4 的模塊高度限制將放寬到 775 微米,有利于繼續使用 TC-NCF。

三星正努力降低 TC-NCF 工藝的晶圓間隙,目標在 HBM4 中將這一高度縮減至 7.0 微米以內。

不過 TC-NCF 技術也面臨著質疑。Dae Woo Kim 回擊稱三星電子的方案相較競爭對手 SK 海力士的 MR-RUF 更適合 12 層乃至 16 層的高堆疊模塊