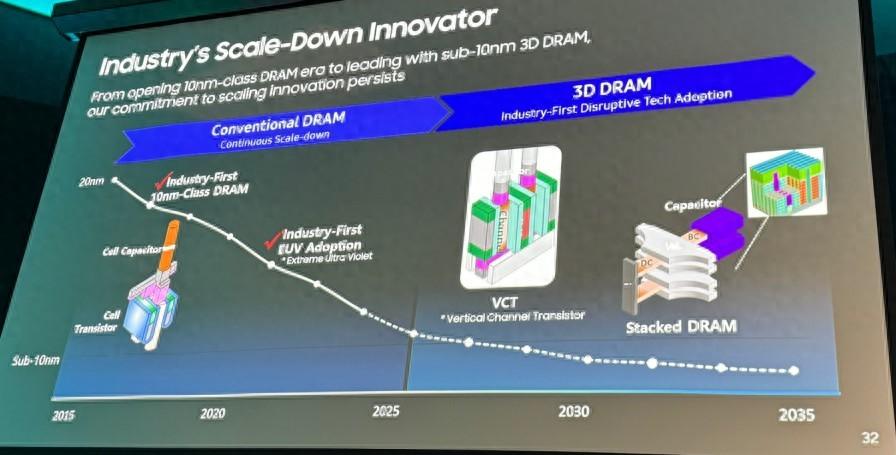

4 月 1 日消息,據(jù)外媒 Semiconductor Engineering 報道,三星電子在行業(yè)會議 Memcon 2024 上表示計劃于 2025 年后在業(yè)界率先進入 3D DRAM 內(nèi)存時代。

DRAM 內(nèi)存行業(yè)將于本十年后期將線寬壓縮至 10nm 以下。而在如此精細的尺度下,現(xiàn)有設(shè)計方案難以進一步擴展,業(yè)界因此正在探索包括 3D DRAM 在內(nèi)的多種創(chuàng)新型內(nèi)存設(shè)計。

▲ 圖源 Semiconductor Engineering

三星在 Memcon 2024 的幻燈片上展示了兩項 3D DRAM 內(nèi)存新技術(shù),包括垂直通道晶體管(Vertical Channel Transistor)和堆疊 DRAM(Stacked DRAM)。

相較于傳統(tǒng)的晶體管結(jié)構(gòu),垂直通道晶體管將溝道方向從水平變?yōu)榇怪保纱蠓鶞p少器件面積占用,但提升了對刻蝕工藝精度的要求。

相較現(xiàn)有 2D DRAM 結(jié)構(gòu),堆疊 DRAM 可充分利用 z 方向空間,在較小面積中容納更多存儲單元,單芯片容納提升至 100G 以上。

3D DRAM 市場有望于 2028 年達到 1000 億美元(IT之家備注:當(dāng)前約 7240 億元人民幣)。為了同其他主要內(nèi)存制造商競爭,三星已于今年初在美國硅谷開設(shè)了一家新的 3D DRAM 研發(fā)實驗室。